CMOS實現Y=AB+C電路的原理與版圖設計

集成電路設計是現代電子技術的核心,其中CMOS技術因其低功耗、高集成度和抗干擾能力強等優點,成為當前主流的集成電路制造工藝。本次課程設計旨在通過CMOS技術實現邏輯函數Y=AB+C,并完成相應的版圖設計。

一、電路原理與CMOS實現

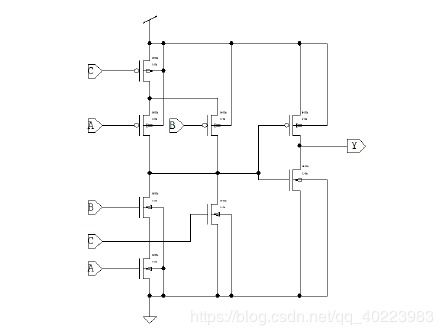

邏輯函數Y=AB+C表示Y等于A與B的乘積再與C進行或運算。在CMOS技術中,該函數可以通過組合邏輯門電路實現。具體來說,使用一個二輸入與門(AND)和一個二輸入或門(OR)構建電路:

- 與門部分:晶體管NMOS和PMOS構成與邏輯,當A和B均為高電平時,輸出高電平。

- 或門部分:晶體管連接實現或邏輯,當A、B或C中任意一個為高電平時,輸出高電平。

CMOS實現的關鍵在于利用上拉網絡(PUN)和下拉網絡(PDN):

- PUN使用PMOS晶體管,當輸入為低電平時導通。

- PDN使用NMOS晶體管,當輸入為高電平時導通。

對于Y=AB+C,PUN設計為(A和B)或C的互補形式,PDN設計為AB或C的直接形式,確保邏輯功能正確且靜態功耗低。

二、版圖設計步驟與要點

版圖設計是將電路邏輯轉化為物理布局的過程,需考慮工藝規則、寄生效應和可靠性:

- 晶體管布局:根據CMOS工藝,NMOS和PMOS晶體管需分開布置,通常NMOS位于襯底,PMOS位于N阱中。每個晶體管需設置適當的寬長比(W/L),以優化速度和功耗。

- 互聯設計:使用金屬層連接晶體管,減少寄生電阻和電容。對于Y=AB+C,需合理布線,避免信號串擾和延遲。例如,A、B、C輸入信號通過多晶硅或金屬1層連接,輸出Y通過高層金屬引出。

- 設計規則檢查(DRC):確保版圖符合代工廠的工藝約束,如最小線寬、間距和覆蓋規則。

- 電路仿真:使用工具如SPICE進行前仿真和后仿真,驗證邏輯功能和時序特性。

三、設計挑戰與優化

在CMOS實現Y=AB+C時,可能面臨面積、速度和功耗的權衡:

- 面積優化:通過共享晶體管或使用復合門減少器件數量。

- 速度提升:調整晶體管尺寸,降低關鍵路徑的延遲。

- 功耗控制:采用低功耗設計技術,如電源門控。

版圖需考慮匹配性和噪聲容限,例如對稱布局以減小工藝偏差的影響。

四、總結

通過本課程設計,學生可以深入理解CMOS技術的基本原理,掌握從邏輯函數到版圖實現的完整流程。Y=AB+C電路作為簡單示例,有助于培養集成電路設計的實踐能力,為后續復雜電路設計奠定基礎。在當今半導體產業中,此類技能對于開發高效、可靠的芯片至關重要。

如若轉載,請注明出處:http://m.jsfjhs.cn/product/37.html

更新時間:2026-05-02 08:08:54