從零開始 設(shè)計一款定制單片機所需的知識體系與核心步驟

在當(dāng)今萬物互聯(lián)的時代,單片機作為嵌入式系統(tǒng)的核心,驅(qū)動著從智能家電到工業(yè)控制的無數(shù)設(shè)備。若想從零開始設(shè)計一款屬于自己的單片機,這無疑是一項融合了硬件與軟件、理論與工程的宏大挑戰(zhàn)。它要求設(shè)計者不僅要有扎實的集成電路(IC)設(shè)計知識,還需遵循一套嚴謹?shù)拈_發(fā)流程。本文將系統(tǒng)性地闡述所需的知識體系與核心設(shè)計步驟。

第一部分:必備的核心知識體系

設(shè)計一款單片機,遠非僅僅是連接幾個邏輯門。它要求一個跨學(xué)科、深層次的知識結(jié)構(gòu):

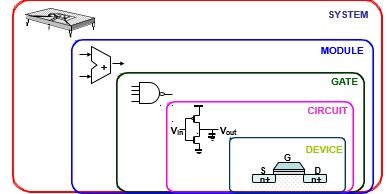

- 半導(dǎo)體物理與器件基礎(chǔ):理解晶體管(尤其是MOSFET)的工作原理、特性曲線、開關(guān)速度與功耗,這是所有集成電路的基石。

- 數(shù)字電路與計算機體系結(jié)構(gòu):精通組合邏輯與時序邏輯設(shè)計。必須深入理解CPU核心架構(gòu)(如基于RISC的ARM Cortex-M系列或自定指令集的微架構(gòu)),包括算術(shù)邏輯單元(ALU)、寄存器堆、控制單元、總線結(jié)構(gòu)以及中斷系統(tǒng)的設(shè)計。

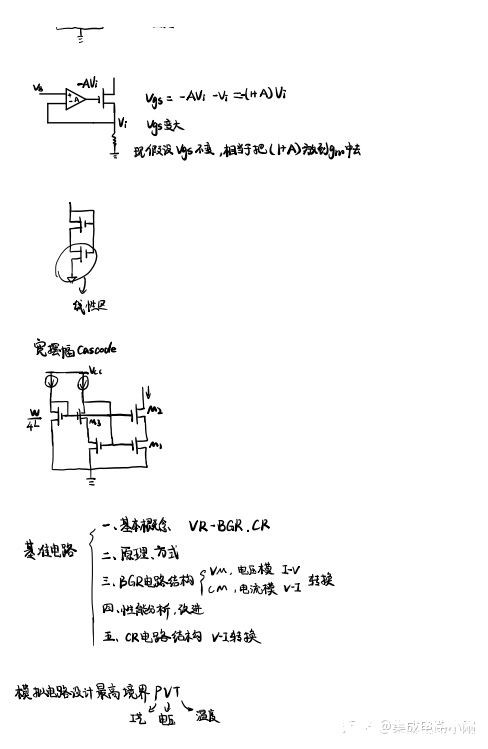

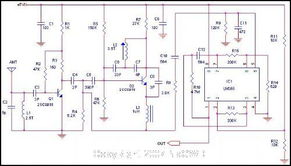

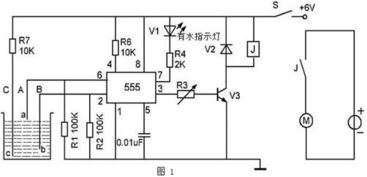

- 模擬與混合信號電路基礎(chǔ):單片機并非純數(shù)字芯片。需要設(shè)計內(nèi)部振蕩器、電源管理模塊、復(fù)位電路、模數(shù)轉(zhuǎn)換器(ADC)等模擬模塊,這要求具備運算放大器、比較器、振蕩電路等知識。

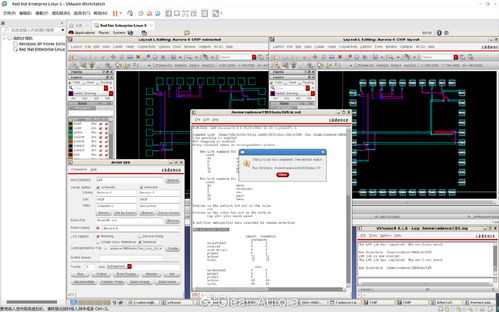

- 硬件描述語言(HDL)與EDA工具:熟練掌握VHDL或Verilog HDL是進行數(shù)字電路設(shè)計、仿真和綜合的必備技能。必須能使用行業(yè)標(biāo)準(zhǔn)的電子設(shè)計自動化(EDA)工具鏈,如Synopsys、Cadence或Mentor(現(xiàn)Siemens EDA)的工具,進行邏輯綜合、布局布線、時序分析和物理驗證。

- 存儲器技術(shù):了解不同存儲器(如Flash用于程序存儲,SRAM用于數(shù)據(jù)存儲)的電路結(jié)構(gòu)、讀寫時序及嵌入方法。

- 低功耗設(shè)計技術(shù):對于現(xiàn)代單片機至關(guān)重要,涉及時鐘門控、電源門控、多電壓域、動態(tài)電壓頻率調(diào)節(jié)(DVFS)等先進技術(shù)。

- 制造與工藝知識:了解芯片的制造流程(光刻、刻蝕、離子注入等)以及特定工藝節(jié)點(如40nm, 28nm)的設(shè)計規(guī)則(DRC)、電氣規(guī)則(ERC)和模型文件。

- 嵌入式軟件與工具鏈:設(shè)計完成后,需為其開發(fā)編譯器(如GCC端口)、匯編器、鏈接器、調(diào)試器以及啟動代碼(Bootloader),這需要編譯原理和系統(tǒng)軟件的知識。

第二部分:從零到一的集成電路設(shè)計核心步驟

設(shè)計流程是一個高度迭代和驗證的過程,主要可分為以下幾個階段:

第1步:需求定義與架構(gòu)設(shè)計

明確單片機的目標(biāo)應(yīng)用:需要多大的處理能力(位寬、主頻)?需要多少Flash和RAM?需要哪些外設(shè)(UART, SPI, I2C, ADC, PWM等)?需要何種功耗水平?基于此,定義指令集架構(gòu)(ISA),是采用現(xiàn)有架構(gòu)(如RISC-V)還是自定義?并規(guī)劃芯片的整體模塊劃分與總線架構(gòu)(如AHB/APB)。

第2步:模塊設(shè)計與RTL編碼

使用Verilog/VHDL,將架構(gòu)轉(zhuǎn)化為寄存器傳輸級(RTL)描述。這包括分別設(shè)計CPU核心、存儲器控制器、外設(shè)IP以及內(nèi)部互聯(lián)總線。此階段需同步編寫全面的測試平臺(Testbench)進行功能仿真,確保每個模塊行為正確。

第3步:前仿真與功能驗證

在EDA仿真環(huán)境中,對整合后的整個RTL設(shè)計進行大規(guī)模仿真測試,運行指令集測試序列和外設(shè)交互測試,確保邏輯功能百分百符合架構(gòu)定義。

第4步:邏輯綜合與門級網(wǎng)表生成

使用綜合工具(如Design Compiler),將RTL代碼映射到目標(biāo)工藝庫的標(biāo)準(zhǔn)邏輯單元(如與門、或門、觸發(fā)器等),生成門級網(wǎng)表。此時需要設(shè)定時鐘頻率、面積、功耗等約束條件。

第5步:后端物理設(shè)計

這是將邏輯變?yōu)槲锢戆鎴D的關(guān)鍵步驟:

- 布局規(guī)劃:確定芯片核心區(qū)域、模塊擺放位置及I/O引腳排列。

- 布局與時鐘樹綜合:放置標(biāo)準(zhǔn)單元,并構(gòu)建低歪斜的全局時鐘分布網(wǎng)絡(luò)。

- 布線:完成單元之間所有信號的金屬連線。

- 物理驗證:進行設(shè)計規(guī)則檢查(DRC)、版圖與原理圖對照(LVS)、電氣規(guī)則檢查(ERC)以及信號完整性分析,確保版圖符合晶圓廠要求且功能正確。

第6步:后仿真與時序簽核

從最終版圖中提取包含布線延遲的精確參數(shù)(如SDF文件),反標(biāo)回仿真環(huán)境進行后仿真。進行靜態(tài)時序分析(STA),確保在所有工藝角(PVT)下均無建立時間和保持時間違規(guī),達到時序閉合。

第7步:流片與封裝測試

將最終確認的版圖數(shù)據(jù)(GDSII文件)交付給晶圓廠(如TSMC、SMIC)進行制造(即“流片”)。芯片制造完成后,進行切割、封裝,隨后在專用測試設(shè)備上進行嚴格的芯片測試,驗證其實際電氣特性和功能。

第8步:軟件開發(fā)與系統(tǒng)集成

為制造成功的芯片移植或開發(fā)完整的軟件開發(fā)工具鏈(SDK)、驅(qū)動程序庫及示例程序,使其能夠被嵌入式工程師真正使用。

###

從零設(shè)計一款單片機是一項周期漫長(通常以年計)、投入巨大的系統(tǒng)工程,涉及數(shù)百個精密環(huán)節(jié)。對于個人或小團隊而言,更現(xiàn)實的起點或許是基于開源架構(gòu)(如RISC-V),使用FPGA進行原型驗證,或從設(shè)計某個外設(shè)IP核開始。理解這一完整知識體系和流程,不僅能深化對計算機系統(tǒng)本質(zhì)的認識,更是邁向高端芯片設(shè)計領(lǐng)域的必經(jīng)之路。它代表了一種對技術(shù)深度與廣度的極致追求,是硬件工程師的終極挑戰(zhàn)之一。

如若轉(zhuǎn)載,請注明出處:http://m.jsfjhs.cn/product/50.html

更新時間:2026-05-04 07:00:24